当前电子产品发展迅速,产品体积向轻、薄、小的方向发展,产品功能又不断增加,对核心部分PCBA功能的要求越来越复杂,体积是越来越小,从而对半导体和封装的集成度要求越来越高。

封装工艺从单一DIE COB工艺-MCM-SIP(多DIE堆叠)-2.5D/3D封装日益复杂化,IC结构也由简单功能转向具备更多和更为复杂的功能,目前,SoC 作为系统级集成电路,能在单一硅芯片上实现信号采集、转换、存储、处理和I/O 等功能,将数字电路、存储器、MPU、MCU、DSP 等集成在一块芯片上实现一个完整系统的功能。芯片工艺也从传统的90nm向22nm转换,甚至14nm-7nm。

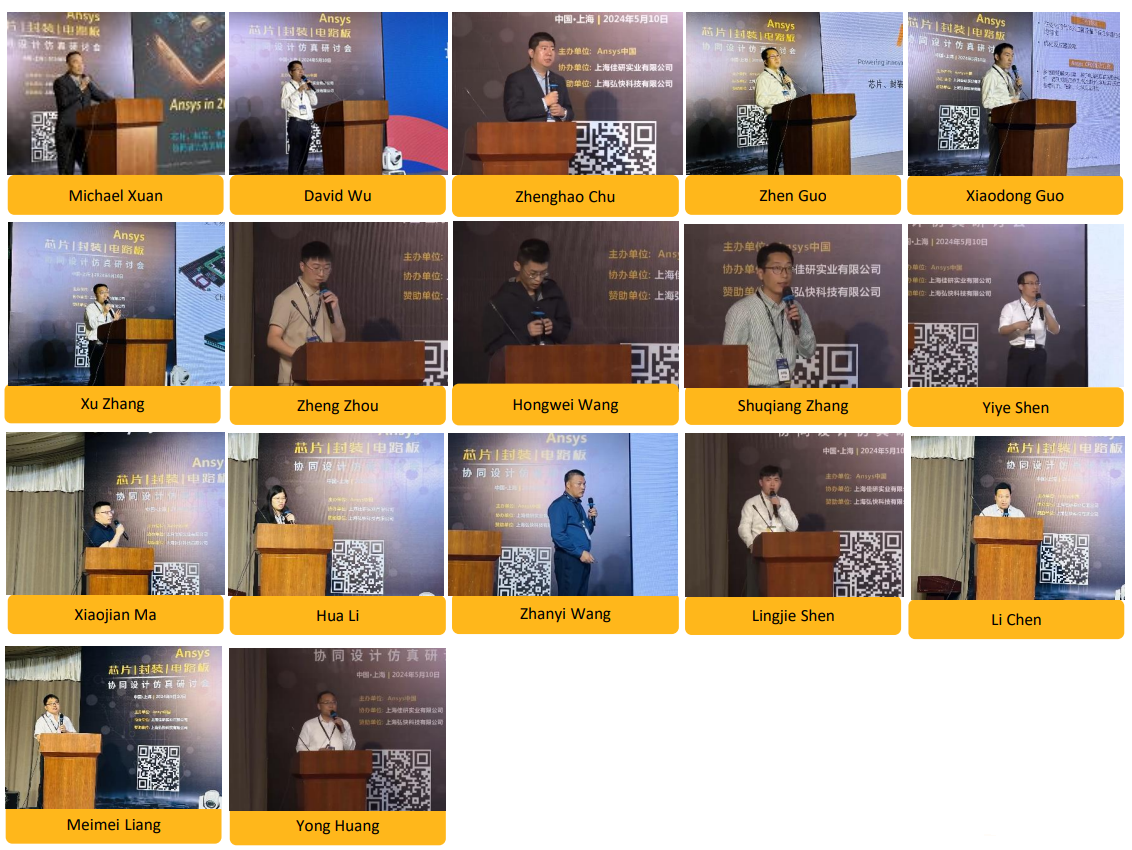

电路设计难度越来越大,生产工艺也越来越复杂,对设计者来说,小型化高速多功能电子产品,以及新的生产工艺,让过去设计仿真经验面临挑战。面对当前产品动能化、体积小型化、信号高速化等挑战,单一的从PCB设计角度去考虑问题,已经无法解决我们当前或今后的问题,必须具备新的系统的设计仿真分析。5月10日,上海佳研与Ansys联合举办的研讨会——Ansys芯片-封装-电路板协同设计仿真在上海举行,将结合Ansys仿真平台和RedEDA设计平台,和大家共同讨论芯片-封装-电路板协同设计仿真分析,包括芯片低功耗分析、芯片封装设计方法、PCB设计方法、封装-PCBSI/PI分析、电磁兼容分析、热仿真分析、应力分析、光学分析、可靠性分析等。

邀请了半导体、芯片设计、芯片加工、封装设计、封装加工、通信、高科技、电力电子、航空、航天、轨道交通、汽车行业等相关单位研发部、测试部、质量部等部门负责人、工程师或其他感兴趣人员参加会,共同探讨,共享技术发展。

![]()

版权所有© 2015 上海佳研实业有限公司 All Rights Reserved 沪ICP备15014036号-1